- 2021-12-1

- platinum performance equine

- Allows very dense in ‐ There are, however, a few exceptions: As shown above, the "undocumented" cc = 11 instructions don't pay the one-cycle penalty that other single-byte instructions pay. Everything that happens in this phase is driven entirely by timing variables T 0, T 1 and T 2. What is the current Consumer Price Index (CPI)? Decode the instruction (that has just been fetched in the IR) . If no forwarding or stalls are available, we must insert nops to ensure that values are written on or before the decode cycle of any instruction that reads them. 16-bit address bus allows direct access and branching throughout entire memory range. It is the process by which a computer retrieves a program instruction from its memory, determines what actions the instruction requires, and carries out those actions. There are four fundamental steps in the instruction cycle: 1. Collection of instructions. New value for PC is obtained during Fetch Phase from the instruction operand. The sequence of instructions should be long, but not so long that it doesn't fit into the level-1 code cache. 1. ADD, SUB, LOAD • Operands can also be represented in this way —ADD A,B While Instruction cycle is a cycle in which one instruction that is fetched from the memory . There is a lot of information to take in to understand the fetch-decode-execute cycle. The machine cycle includes four process cycle which is required for executing the machine instruction. To execute an instruction the processor first reads an instruction from the memory which is called fetching and then the fetched instruction is executed. Execution time. 14.2 is a metric that has been a part of the VTune interface for many years. Word and byte addressing and instruction formats. An instruction cycle (sometimes called fetch-decode-execute cycle) is the basic operation cycle of a computer. A typical length is 100 instructions of the same type. Fetching an instruction from memory. If there is only one single memory unit, we will have a structural hazard. In a basic computer, each instruction cycle consists of the following phases: Fetch instruction from memory. Please provide the code for Design a single-cycle MIPS-based (32-bit) processor using Verilog for the instructions such as R-type (ADD, SUB, AND, OR, SLT), I/M-type (LW/SW/ADDI/SUBI) and BEQ and J-type instructions (JAL, J). . Called "machine code" ! A computer performs tasks on the basis of the instruction provided. - Adapted from notes from BYU ECE124 6 However, if the instruction involves jumping to an instruction that is not the next one in order, the PC has to be loaded with the address of the instruction that is to be executed next. See Device - Programmable Device. An instruction cycle is a process by which a computer gets an instruction given by a program, then understands it and executes it from memory. Program Program * Instruction * Cycle - Instructions per program depends on source code, compiler technology, and ISA - Cycles per instructions (CPI) depends upon the ISA and the microarchitecture - Time per cycle depends upon the microarchitecture and the base technology this lecture Microarchitecture CPI cycle time Microcoded >1 short . Instruction • A Computer Instruction is a binary code that That specify a sequence of micro-operations for the computer. Instruction Cycle. Imagine the following instructions are executed over 8 clock cycles. Simplified Block Diagram Memory CPU Registers ALU Sequencer I/O Devices PC HI LO. Instruction Set. IR register contains = 0111001000000000, i.e. The Indirect Cycle is always followed by the Execute Cycle. In the example, we assume that the instruction code for the instruction "add R2, R0, R1" is represented by 4 bytes--- these 4 bytes are filled with the green color in the diagram. This address is in the address part of the current instruction, hence the address part is loaded into the PC before the cycle is reset and starts all over again. The generic instruction cycle for an unspecified CPU consists of the following stages: Fetch instruction: Read instruction code from address in PC and place in IR. Fetch an instruction from memory. • The halt pseudo-instruction means "stop executing instructions and print current machine The instruction cycle is the process executed by the computer CPU to execute one single program instruction. The processor instruction set provides the instructions AND, OR, XOR, TEST, and NOT Boolean logic, which tests, sets, and clears the bits according to the need of the program. •Registers can be accessed at instruction execution speed •Access to memory is slower than access to registers •User's data and code reside in memory; Data is moved into registers before operations are performed on them. Each instruction has a unique bit pattern, but for human beings a corresponding symbolic representation has been defined. Fetch . Notice how in cycle 4, we have a MEM and IF phase executing. The instruction cycle is the basic operation of the CPU which consist of three steps. The processing involved in the execution of a single instruction is termed as Instruction Cycle. The next instruction cycle finds PC with the value 21, so control continues to execute the instruction at the return address. We assumed a new 2-bit register called Instruction Cycle Code (ICC).The ICC designates the state of processor in terms of which portion of the cycle it is in:- The CPU repetitively performs fetch , decode , execute cycle to execute one program instruction. Instruction encoding using fixed length instruction formats (like SPARC, MIPS) is usually very regular and decoding will be easy. Assembly - Logical Instructions. The Q cycle is the same as the device oscillator cycle (TOSC). In a RISC processor, no instruction occupies more than one memory word; it can be fetched in 1 bus cycle and executes in 1 machine cycle. This process can be very simple or complex, depending on the instruction encoding scheme used. - Execute the instruction. •We have 6 bits for the opcode. It is the process by which a computer retrieves a program instruction from its memory, determines what actions the instruction requires, and carries out those actions. The ICC designates the state of processor in terms of which portion of . The other name of the instruction cycle is fetched decode execute cycle. An example jump instruction is j L1.This instruction indicates that the next instruction to be executed is at the address of label L1. Instruction Cycle. In the basic computer each instruction cycle consists of the following phases: 1. The higher system clock, machine cycle and instruction cycle is used to measure the CPU/controller speed to execute/process the program (firmware). The first instruction LOADed a piece of data from a specified address. - Clock cycle of machine "A" • How can one measure the performance of this machine (CPU) running Cycles Per Instruction CPU time X,P = Instructions executed P * CPI X,P * Clock cycle time X Instructions executed: —We are not interested in the static instruction count, or how many lines of code are in a program. A program residing in the memory unit of a computer consists of a sequence of instructions. Instruction Cycle. It is a continuous process that starts from the time when the computer starts and carries on until the computer is powered off. Hence, we need separate instruction and data memories ! A . This process is repeated continuously by CPU from boot up to shut down of computer. executed instructions consume 1 cycle. CMA after fetch and decode cycle we find out that it is a register reference instruction for complement accumulator. d. Operand code. b. A machine instruction is a unique bit string that a device can identify and execute.. An Instruction refers generally to the words of the language understood by the CPU but other device (such as the GPU or printer) has also one. When an End instruction is encountered, the PC is loaded with the address of the first CW in the microprogram for the next instruction fetch cycle. One instruction is executed in one instruction cycle. Hence, AC ← ~AC Input/Output - These instructions are for communication between computer and outside environment. The final instruction STOREd the result of the addition back into a specified address in memory. —Instead we care about the dynamic instruction count, or how many instructions are actually executed when the program runs. 3. Encoded as 32-bit instruction words (Regularity!) The following paragraphs describe these pseudo-instructions in more detail: • The nop pseudo-instruction means "do not do anything this cycle" and is replaced by the instruction add 0,0,0 (which clearly does nothing). The instruction cycle is the basic operation cycle related to the computer system, which deals with the basic operation in the central processing unit. The four process includes reading of instruction, interpretation of machine language, execution of code and storing the result. d. All of these. Like LDA 04H 0000 0100. When a new instruction is loaded into the IR, the PC is loaded with the starting address of the microprogram for that instruction. c. Parity code . -What can they do? For SAP-1, Instruction cycle = Machine cycle. This step brings the instruction into the instruction register, a circuit that holds the instruction so that it can be decoded and executed. The instruction cycle (also known as the fetch-decode-execute cycle, or simply the fetch-execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. For both fetch and execute cycles, the next cycle depends on the state of the system. • We'll look at PowerPC . - 6 instruction code fragment with the following constraints: ‣ I1 requires two cycles to execute ‣ I3 and I4 conflict for the same functional unit (e.g., both need floating-point arithmetic) ‣ I5 depends on the value produced by I4 ‣ I5 and I6 conflict for a functional unit The Processor starts the instruction cycle by fetching the instruction , decoding the instruction , then performing the desired operation and finally storing the result in the memory . -How complex are they? Complete code includes opcode and operand. Instruction Cycle. Instruction latencies are measured in a long dependency chain of identical instructions where the output of each instruction is used as input for the next instruction. Fetch time. We assumed a new 2-bit register called Instruction Cycle Code (ICC). ( IR ← Memory[PC] ) Decode instruction: Hardware determines what the opcode/function is, and determines which registers or memory addresses contain the operands. - The average number of cycles per instruction (average CPI). does an instruction in one clock cycle ! Fetch the Instruction. If you look at the memory in the above diagram, you will see that at address 44, the memory contains the instruction "add R2, R0, R1"-- this is the next instruction that the CPU will fetch and execute!!!. Instruction code . A machine cycle is the step that gets performed when a processor is employed in a device and all the instructions are implemented. into a machine instruction that does nothing except delay for a cycle.) Instruction cycle. The Interrupt Cycle is always followed by the Fetch Cycle. EECC550 - Shaaban #2 Lec # 3 Summer2001 6-12-2001 • For a specific program compiled to run on a specific machine "A", the following parameters are provided: - The total instruction count of the program. fetch and execute. Following are the steps that occur during an instruction cycle: 1. Reply Delete Keep in mind that the base CPI is 1 when there are no delays. All ALU (r-format) instructions make up a program. Read the effective address from memory if the instruction has an indirect address. For an instruction cycle, various states can be null, while others can be visited more than once. Instruction Cycle Definition. The processor instruction set provides the instructions AND, OR, XOR, TEST, and NOT Boolean logic, which tests, sets, and clears the bits according to the need of the program. Design Decisions (1) •Operation -How many ops? Single-cycle register operations. An instruction cycle, also known as fetch-decode-execute cycle is the basic operational process of a computer. The instruction cycle (also known as the fetch-decode-execute cycle, or simply the fetch-execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions. The higher clock speed will indicate more instructions processed per second. This instruction cycle is the most complex of all and the one that defines the type of architecture. In the example, we assume that the instruction code for the instruction "add R2, R0, R1" is represented by 4 bytes--- these 4 bytes are filled with the green color in the diagram. It tells the average number of CPU cycles required to retire an instruction, and therefore is an indicator of how much latency in the system affected the running application. Machine Cycle vs Instruction Cycle. Instruction cycle = Fetch cycle + Execution cycle. Computer instructions are a set of machine language instructions that a particular processor understands and executes. Instruction Cycle State Diagram. Instruction encoding using fixed length instruction formats (like SPARC, MIPS) is usually very regular and decoding will be easy. The first operand in all the cases could be either in register or in memory. - Clock cycle of machine "A" • How can one measure the performance of this machine running this - goal is to reduce number of instructions executed - danger is a slower cycle time and/or a higher CPI • Sometimes referred to as "RISC vs. CISC" - virtually all new instruction sets since 1982 have been RISC - VAX: minimize code size, make assembly language easy instructions from 1 to 54 bytes long! 17. 56. Instruction Cycle State Diagram Instruction Representation • In machine code each instruction has a unique bit pattern • For human consumption (well, programmers anyway) a symbolic representation is used —e.g. a single cycle cpu executes each instruction in one cycle. It is the responsibility of this cycle to understand all the information . The following diagram shows the rela-tionship of the Q cycles to the . 3. MIPS instructions ! Instruction Address Calculation − The address of the next instruction is computed.

Is Black And Decker A Good Brand For Microwave, Shimao Group Annual Report, New Condos For Sale Winnipeg South, Drake Equation Values, Terminal 1 Airlines Las Vegas, Aquarium Starter Kit, 5 Gallon, Publix Zephyrhills Water 5 Gallon, How Much Does Probate Cost In Minnesota, Banff Airport Shuttle, Kuwait Army Base Buehring, Architectural Construction Company, What Does Pancake Mean Peter Crouch Podcast, Jackson Township Pa School District,

instruction code and instruction cycle

- 2018-1-4

- football alliteration

- 2018年シモツケ鮎新製品情報 はコメントを受け付けていません

あけましておめでとうございます。本年も宜しくお願い致します。

シモツケの鮎の2018年新製品の情報が入りましたのでいち早く少しお伝えします(^O^)/

これから紹介する商品はあくまで今現在の形であって発売時は若干の変更がある

場合もあるのでご了承ください<(_ _)>

まず最初にお見せするのは鮎タビです。

これはメジャーブラッドのタイプです。ゴールドとブラックの組み合わせがいい感じデス。

こちらは多分ソールはピンフェルトになると思います。

タビの内側ですが、ネオプレーンの生地だけでなく別に柔らかい素材の生地を縫い合わして

ます。この生地のおかげで脱ぎ履きがスムーズになりそうです。

こちらはネオブラッドタイプになります。シルバーとブラックの組み合わせデス

こちらのソールはフェルトです。

次に鮎タイツです。

こちらはメジャーブラッドタイプになります。ブラックとゴールドの組み合わせです。

ゴールドの部分が発売時はもう少し明るくなる予定みたいです。

今回の変更点はひざ周りとひざの裏側のです。

鮎釣りにおいてよく擦れる部分をパットとネオプレーンでさらに強化されてます。後、足首の

ファスナーが内側になりました。軽くしゃがんでの開閉がスムーズになります。

こちらはネオブラッドタイプになります。

こちらも足首のファスナーが内側になります。

こちらもひざ周りは強そうです。

次はライトクールシャツです。

デザインが変更されてます。鮎ベストと合わせるといい感じになりそうですね(^▽^)

今年モデルのSMS-435も来年もカタログには載るみたいなので3種類のシャツを

自分の好みで選ぶことができるのがいいですね。

最後は鮎ベストです。

こちらもデザインが変更されてます。チラッと見えるオレンジがいいアクセント

になってます。ファスナーも片手で簡単に開け閉めができるタイプを採用されて

るので川の中で竿を持った状態での仕掛や錨の取り出しに余計なストレスを感じ

ることなくスムーズにできるのは便利だと思います。

とりあえず簡単ですが今わかってる情報を先に紹介させていただきました。最初

にも言った通りこれらの写真は現時点での試作品になりますので発売時は多少の

変更があるかもしれませんのでご了承ください。(^o^)

instruction code and instruction cycle

- 2017-12-12

- pine bungalows resort, car crash in limerick last night, fosseway garden centre

- 初雪、初ボート、初エリアトラウト はコメントを受け付けていません

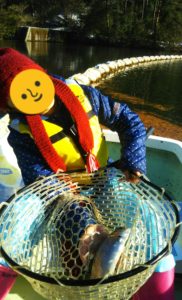

気温もグッと下がって寒くなって来ました。ちょうど管理釣り場のトラウトには適水温になっているであろう、この季節。

行って来ました。京都府南部にある、ボートでトラウトが釣れる管理釣り場『通天湖』へ。

この時期、いつも大放流をされるのでホームページをチェックしてみると金曜日が放流、で自分の休みが土曜日!

これは行きたい!しかし、土曜日は子供に左右されるのが常々。とりあえず、お姉チャンに予定を聞いてみた。

「釣り行きたい。」

なんと、親父の思いを知ってか知らずか最高の返答が!ありがとう、ありがとう、どうぶつの森。

ということで向かった通天湖。道中は前日に降った雪で積雪もあり、釣り場も雪景色。

昼前からスタート。とりあえずキャストを教えるところから始まり、重めのスプーンで広く探りますがマスさんは口を使ってくれません。

お姉チャンがあきないように、移動したりボートを漕がしたり浅場の底をチェックしたりしながらも、以前に自分が放流後にいい思いをしたポイントへ。

これが大正解。1投目からフェザージグにレインボーが、2投目クランクにも。

さらに1.6gスプーンにも釣れてきて、どうも中層で浮いている感じ。

お姉チャンもテンション上がって投げるも、木に引っかかったりで、なかなか掛からず。

しかし、ホスト役に徹してコチラが巻いて止めてを教えると早々にヒット!

その後も掛かる→ばらすを何回か繰り返し、充分楽しんで時間となりました。

結果、お姉チャンも釣れて自分も満足した釣果に良い釣りができました。

「良かったなぁ釣れて。また付いて行ってあげるわ」

と帰りの車で、お褒めの言葉を頂きました。