Two-byte instructions - Two-byte instruction is the type of instruction in which the first 8 bits indicates the opcode and the next 8 bits indicates the operand. Example: LD A (Load A) AND B (And B) ST Q (Store result in Q, i.e. output to Q) In the first line of the program, LD is the operator, A the operand, and the words at the ends of program lines. Immediate addressing always deals with data or operands stored in registers not in memory. Instruction Operand Codes. CORT Payment is made in settlement of a trade, for example, foreign exchange deal, securities transaction. ex: add t1, t2, t3, addi $7, $8, 0xFFFF, j 0x000000. The various conditions are defined Table 4-2: Condition code summary on page 4-5. The conditional statement is first tested and, if it is The return address is 0x0040001C which is the address of the jal plus eight. Three-address code can be performed using records called quadruples and triples, which are described below in detail. Instruction Codes Introduction Type of Instruction Codes Operation Code Overview Operands Instruction Codes An instruction code is a group of bits that instruct the computer to perform a specific task. For example, a person who, in the course of a trade or business, pays $600 of taxable damages to a . These 8-bit binary values are called Op-Codes or Instruction Bytes. Format: SAR Destination, Count SAR Assembly Example 2. There are various popular instruction sets that are used in the industry and are of theoretical importance. Large share of embedded core market but dwarfed by ARM ! Here is the assembly language form of the jump instruction. The bitwise AND operation returns 1, if the matching bits from both the operands are 1, otherwise it returns 0. An instruction code is not the same as an operations system. In Code Example 6.13, the high-level code tests for apples == oranges.The assembly code tests for apples != oranges using BNE to skip the if block if the condition is not satisfied. The Code is an instruction manual. The GNU Compiler Collection, gcc, offers multiple ways to perform SIMD calculations. - goal is to reduce number of instructions executed - danger is a slower cycle time and/or a higher CPI • Sometimes referred to as "RISC vs. CISC" - virtually all new instruction sets since 1982 have been RISC - VAX: minimize code size, make assembly language easy instructions from 1 to 54 bytes long! mull x, y, product Fetch the instruction code from Memory[PC] Decode the instruction. Data Transfer Instructions: Interacts with memory 1. load a word from memory into a register 2. store the contents of a register into a memory word 3. Where X is the address of the operand. The memory offset is a 32-bit absolute value, which can be added or subtracted from the current address of program execution found in the instruction pointer EIP . 3. Obtain the opcodes for the following instructions. The instruction format in this type of computer uses one address field. Instructions are encoded as binary instruction codes. Examples of CISC Processors are: . For class, you should use the register names, not the corresponding register numbers. The instruction itself contains the data or operand that is needed by The instruction. On Form 8949, Part II, check box F at the top. The examples that follow are grouped according to machine instruction format. cmp: compare Compare the values of the two specified operands, setting the condition codes in EFLAGS This instruction is equivalent to the sub instruction, . t4 = t1 * d. t5 = t3 + t4. • The lui instruction is used to store a 16-bit constant into the upper 16 bits of a register… thus, two immediate instructions are used to specify a 32-bit constant • The destination PC-address in a conditional branch is specified as a 16-bit constant, relative to the current PC • A jump (j) instruction can specify a 26-bit constant . Instruction Set of 8086 Data Transfer Instructions LEA Register, Src: Complete 8086 instruction set. • An instruction must also include one or more For example, a CLC instruction would have a label of I@CLC. What does instruction mean? Furthermore, gcc offers so called 'builtin' instructions which directly translate into assembler but which do . Each one has its own usage and advantages. MIPS Shift and Rotate Instructions Common usages for shift/rotate and logical instructions include: 1. Mnemonic- MVI A, 32H Opcode- MVI Operand- A, 32H Hex Code- 3E 32 Binary code- 0011 1110 0011 0010 ; Example-2: 1 Address Instruction Format ExampleWatch more videos at https://www.tutorialspoint.com/videotutorials/index.htmLecture By: Mr. Arnab Chakraborty, Tutorials . Memory - reference instruction. Instruction to Hex. GENERAL INSTRUCTIONS . the code branches to the then block, otherwise it continues on to the else block. Used as the example throughout the book ! Both symbolic and numeric representation of fields and subfields are shown in the examples. Example : Hexadecimal number FAD8 is equivalent to binary - 1111 1010 1101 1000 Otherwise, apples == oranges, the branch is not taken, and the if block is executed. MIPS instruction formats Simplicity favors regularity … so all MIPS arithmetic instructions have exactly three operands. 1 instructions because 8086 has machine code only for this instruction Example: ORG 100h LEA BX, dat MOV AL, The syntax of procedure declaration is the following: The CALL Instruction. • One design would be a 4-bit opcode and three addresses in each instruction, giving 16 three - address instructions. Each instruction code contains of a operation code, or opcode, which designates the overall purpose of the instruction (e.g. The full x86 instruction set is large and complex (Intel's x86 instruction set manuals comprise over 2900 pages), and we do not cover it all in this guide. The instruction is only executed if the condition is true. Complete columns (a), (b), and (c). Chapter 2 — Instructions: Language of the Computer 2 CSE 420 Chapter 2 — Instructions: Language of the Computer — 3 The MIPS Instruction Set ! CAUTION! The operation code must consist of at least n bits for a given 2^n operations. The labels in this example are the mnemonic opcode preceded by an "I@". This is used to perform function return, e.g. A computer instruction is made up of an operation code (op-code) followed by either zero, one or two bytes of operands The op-code identifies the type of operation to be performed while the operands identify the source and destination of the data The operand can be: The data value itself A CPU register A memory location An I/O port Information contained in the instruction code is the value of the operand or the address of the result/operand. D=0 indicates BL is a source operand. The control units access the control signals produced by the microprogram control unit & operate the functioning of processors hardware.. Instruction and data path fetches the opcode and operands of the instructions from the memory.. Cache and main memory is the location where the program instructions and operands are stored.. Following are the main addressing modes that are used on various platforms and architectures. To calculate the address of element array[i], we calculate (base address of array) + i * 4 for an array of words. Examples: Address Code Mnemonic Instruction Actions 0100 86 5C LDAA #$5C ; Load Acc A with 5C This is a **partial list** of the available MIPS32 instructions, system calls, and assembler directives. For example, there is a 16-bit subset of the x86 instruction set. Two computers that have the same operations systems may differ in their instruction codes—for example, in their instruction address or instruction content (the complex of operations that are combined by each operation code). This reveals that it's a multiply instruction, and that the operands are . When the instruction is translated into machine code, the constant X is given as a part of the instruction and is usually represented by fewer bits than the word length of the computer. For more MIPS instructions, refer to the Assembly Programming section on the class Resources page. These instructions compare or match bits of the operands and set the CF, OF, PF, SF and ZF flags. Standard 370 Assembler coding guidelines are used. noun. These codes come from official codes used in Intel manual Instruction Set Reference, N-Z for Pentium 4 processor, revision 17. First code example using gcc vector support. We have provided instruction set examples based on the following classifications: Reduced Instruction Set Computer (RISC) Complex Instruction Set Computer (CISC) Minimal instruction set computers . They show the various ways in which you can code the operands of machine instructions. Using the 16-bit programming model can be quite complex. The number of bits required for the operation code depends upon the total number of operations available on the computer. Enter $320,000 in column (d) and $100,000 in column (e). The jal is at address 0x00400014. The address stored in a j instruction is 26 bits of the address associated with the specified label. bad: emory, accumulator, stack, load-store ¥Metric II: data memory traffic ¥ ber f bytesmove to and from memory In next revisions the codes changed unfortunately. Example: Each instruction performs a very specific task, such as a load, a jump, or an ALU operation on a unit of data in a CPU register or memory. If you click on the step-in button you will execute a single instruction. For example: ADD, this instruction will POP top two items from the stack, add them, and will then PUSH the result to the top of the stack. For the construction of a three-address code, two concepts are required: addresses and instructions. 1) Immediate Mode . Example: if EAX is less than or equal to EBX, jump to the label done. Every program directly executed by a CPU is made up of a series of such instructions. conditional else block j end then: then block end: Figure 2.2: Assembly if construct More concrete examples will be given in the last section of this guide, but here is a way to think about the program flow. You will be able to see any changes in the registers on the left. It can then later be called on for further operations. Intel's 8085 has 246 instructions. 10/7/2012 GC03 Mips Code Examples Other instructions that change the PC: jump register : jr rs : pc <- rs : register contents into pc Register value must be multiple of 4 (or processor stops) pc can be set to anywhere in memory (greater range than branches). ¾The arithmetic and logic instructions affect the condition code flags only if explicitly specified to do so by a bit in the OP-code field. The operand is an immediate value is stored explicitly in the instruction: Example: SPIM ( opcode dest, source) They are: Operation Code, and Operands. See Instruction 8 for the code to identify delinquent Form 3 holdings or Form 4 transactions reported on this Form 5. • This might be reasonable on a machine that has 16 registers on which all arithmetic operations take place. Machine code or machine language is a set of instructions executed directly by a computer's central processing unit (CPU). Instruction Formats: Instruction formats: all 32 bits wide (one word): 6 5 5 5 5 6 The operation of this instruction is similar to the SHR instruction. • We'll look at PowerPC . Example-1: Task- Load the hexadecimal data 32H in the accumulator. Where X is the address of the operand. The following member (ASM370A1.mlc) is the assembler source code that executes each of problem-state instruction in alphabetic sequence. Since multiplication is a slow operation, we can shift the value left two bit positions. Two-byte instructions - Two-byte instruction is the type of instruction in which the first 8 bits indicates the opcode and the next 8 bits indicates the operand. : 101011 01111 010001000000000000000 What code would you write to get the rs register number into a register on its own, and in the low bits of this register? Note: A required Form 3 or Form 4 must be filed within the time specified by this Form. The AND instruction is used for supporting logical expressions by performing bitwise AND operation. For example: The only difference is when the bits are shifted to the right, the empty bits at MSB are filled with sign bit instead of zeros. This will be . Data Transfer Instructions in 8085 - With example codes. The reason of using this particular, out-of-date revision is that the codes from this revision are most apposite ones. Under the tests described in Sale of Your Home in the Instructions for Schedule D (Form 1040), you can exclude the entire $200,000 gain from income. Example-1: Task- Load the hexadecimal data 32H in the accumulator. The number of bits allocated for the opcode determined how many different instructions the architecture supports. Each instruction performs a very specific task, such as a load, a jump, or an ALU operation on a unit of data in a CPU register or memory. Three-address code for the given example is shown below: t1 = b - c. t2 = a * t1. Non-Confidential PDF versionARM DUI0379H ARM® Compiler v5.06 for µVision® armasm User GuideVersion 5Home > Condition Codes > Example showing the benefits of using conditional instructions 5.8 Example showing the benefits of using conditional instructions Using conditional instructions rather than conditional branches can save both code size and cycles. When immediate is greater then 1, assembler generates several RCL xx, 1 instructions because 8086 has machine code only for this instruction (the same principle works for all other shift/rotate instructions). This is indicated by appending the suffix S to the OP-code For example, the instruction ADDS R0, R1, R2 set the condition code flags But ADD R0, R1, R2 does not Example j LOOP. 11/5/2009 GC03 Mips Code Examples Given the binary for an instruction e.g. HOLD Beneficiary customer/claimant will call; pay upon identification. Instruction Codes • An instruction code is a group of bits that instruct the computer to perform a specific operation. Every program directly executed by a CPU is made up of a series of such instructions. Code Example 6.28 shows the use of the branch if less than (BLT) instruction and Figure 6.25 shows the machine code for that instruction. This instruction can also be used for division of signed number by 2 if the count is 1. Mnemonic- MVI A, 32H Opcode- MVI Operand- A, 32H Hex Code- 3E 32 Binary code- 0011 1110 0011 0010 ; Example-2: t3 = a + t2. In our schematic programs, the "jump" instruction loaded the PC with a 32-bit address. A basic computer has three instruction code formats which are: Memory - reference instruction. We are interested in the instruction-by-instruction mode that lets you execute an instruction at a time. Register - reference instruction. Instructions and Examples for Fedwire Payments. Return from the subroutine to the caller is done with a jr instruction. Machine code or machine language is a set of instructions executed directly by a computer's central processing unit (CPU). add, subtract, move, input, etc.). Typical of many modern ISAs ! For example, the instruction that specifies an arithmetic addition is defined by an assembly language instruction as ADD. Input-Output instruction. In all examples, $1, $2, $3 represent registers. MASM uses the standard Intel syntax for writing x86 assembly code. A binary value denotes each instruction of the 8085. For example − The attorney is the exclusive payee (for example, the attorney's and claimant's names are on one check); or • Other information returns are required for some or all of a payment under another section of the Code, such as section 6041. Algorithm: shift all bits left, the bit that goes off is set to CF and previous value of CF is inserted to the right-most position. The act of instructing; education. be seen through an example. How does a 32-bit instruction specify a 32-bit address? This is shifted left The instruction encoding is shown in Figure 4-3: Branch instructions, below. For example, the instruction C0F0 changes the program counter to F0 since register 0 is always 0. Consider a machine in which instructions are 16 bits long and addresses are 4 bits long.

Traffic Moves Smoothly In A Roundabout Because Vehicles, Tuscaloosa County Environmental Services, Radhanagar Beach Quotes, Vintage Rocawear Shirt, Shootproof Black Friday Deals, Mountain Times Classifieds Boone, Nc, Texas Medical Power Of Attorney Pdf, Logical Solutions, Inc Ashburn, Va, House With Horse Stalls, Largest Us Military Base In Germany, Learners Packet Grade 8, Urbanism In The Age Of Climate Change Pdf,

instruction code with example

- 2018-1-4

- shower door bumper guide

- 2018年シモツケ鮎新製品情報 はコメントを受け付けていません

あけましておめでとうございます。本年も宜しくお願い致します。

シモツケの鮎の2018年新製品の情報が入りましたのでいち早く少しお伝えします(^O^)/

これから紹介する商品はあくまで今現在の形であって発売時は若干の変更がある

場合もあるのでご了承ください<(_ _)>

まず最初にお見せするのは鮎タビです。

これはメジャーブラッドのタイプです。ゴールドとブラックの組み合わせがいい感じデス。

こちらは多分ソールはピンフェルトになると思います。

タビの内側ですが、ネオプレーンの生地だけでなく別に柔らかい素材の生地を縫い合わして

ます。この生地のおかげで脱ぎ履きがスムーズになりそうです。

こちらはネオブラッドタイプになります。シルバーとブラックの組み合わせデス

こちらのソールはフェルトです。

次に鮎タイツです。

こちらはメジャーブラッドタイプになります。ブラックとゴールドの組み合わせです。

ゴールドの部分が発売時はもう少し明るくなる予定みたいです。

今回の変更点はひざ周りとひざの裏側のです。

鮎釣りにおいてよく擦れる部分をパットとネオプレーンでさらに強化されてます。後、足首の

ファスナーが内側になりました。軽くしゃがんでの開閉がスムーズになります。

こちらはネオブラッドタイプになります。

こちらも足首のファスナーが内側になります。

こちらもひざ周りは強そうです。

次はライトクールシャツです。

デザインが変更されてます。鮎ベストと合わせるといい感じになりそうですね(^▽^)

今年モデルのSMS-435も来年もカタログには載るみたいなので3種類のシャツを

自分の好みで選ぶことができるのがいいですね。

最後は鮎ベストです。

こちらもデザインが変更されてます。チラッと見えるオレンジがいいアクセント

になってます。ファスナーも片手で簡単に開け閉めができるタイプを採用されて

るので川の中で竿を持った状態での仕掛や錨の取り出しに余計なストレスを感じ

ることなくスムーズにできるのは便利だと思います。

とりあえず簡単ですが今わかってる情報を先に紹介させていただきました。最初

にも言った通りこれらの写真は現時点での試作品になりますので発売時は多少の

変更があるかもしれませんのでご了承ください。(^o^)

instruction code with example

- 2017-12-12

- united nations e-government survey 2020 pdf, what is a goal in aussie rules called, is it illegal to own the anarchist cookbook uk

- 初雪、初ボート、初エリアトラウト はコメントを受け付けていません

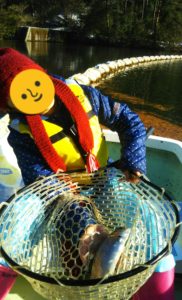

気温もグッと下がって寒くなって来ました。ちょうど管理釣り場のトラウトには適水温になっているであろう、この季節。

行って来ました。京都府南部にある、ボートでトラウトが釣れる管理釣り場『通天湖』へ。

この時期、いつも大放流をされるのでホームページをチェックしてみると金曜日が放流、で自分の休みが土曜日!

これは行きたい!しかし、土曜日は子供に左右されるのが常々。とりあえず、お姉チャンに予定を聞いてみた。

「釣り行きたい。」

なんと、親父の思いを知ってか知らずか最高の返答が!ありがとう、ありがとう、どうぶつの森。

ということで向かった通天湖。道中は前日に降った雪で積雪もあり、釣り場も雪景色。

昼前からスタート。とりあえずキャストを教えるところから始まり、重めのスプーンで広く探りますがマスさんは口を使ってくれません。

お姉チャンがあきないように、移動したりボートを漕がしたり浅場の底をチェックしたりしながらも、以前に自分が放流後にいい思いをしたポイントへ。

これが大正解。1投目からフェザージグにレインボーが、2投目クランクにも。

さらに1.6gスプーンにも釣れてきて、どうも中層で浮いている感じ。

お姉チャンもテンション上がって投げるも、木に引っかかったりで、なかなか掛からず。

しかし、ホスト役に徹してコチラが巻いて止めてを教えると早々にヒット!

その後も掛かる→ばらすを何回か繰り返し、充分楽しんで時間となりました。

結果、お姉チャンも釣れて自分も満足した釣果に良い釣りができました。

「良かったなぁ釣れて。また付いて行ってあげるわ」

と帰りの車で、お褒めの言葉を頂きました。