- 2021-12-1

- lot 100 mango gummy ingredients

Typically an IR has two registers inside it as shown below. Memory buffer register: Here the the data gets stored to transfer or get the data from immedia… View the full answer Transcribed image text : (Program Counter - PC, Instructions Register - IR and Accumulator - AC). MBR: Memory Buffer Register stores instruction and data received from the memory and sent from the memory. It helps in analysing the opcode and operand present in the instruction. The _____ determines the opcode and the operand specifiers. It contains the copy of designated memory locations specified by the memory address register. Instruction Register. Note that these are definitions as per basic. Once the instruction is fetched from memory then fetched instruction is stored in Instruction Register, Decoder is connected with this instruction register and decode the fetched instruction. The main difference between register and buffer is that a register is a temporary storage area in the processor that allows transferring data faster while buffer is a temporary storage area in main . Memory Buffer Register. The Clipper (TM) Processor: instruction set architectures and implementation This register directly drives the address bus and the memory address decoder in RAM or ROM. A) Taking advantage of time wasted by long wait interrupt handling. อ่านค่าจากหน่วยความจำที่มีการเชื่อมต่อกับ Data bus และ instruction register. D) Increasing processor speed. A memory buffer register ( MBR) (also known as memory data register ( MDR )) is the register in a computer 's processor, or central processing unit, CPU, that stores the data being transferred to and from the immediate access storage. Fetch. Register renaming: Associate a "tag"with each data value 2. The internal registers include the instruction register, memory buffer register, memory data register, and memory address register. 9. The instruction word is also called the op code or operation code. The MAR or address buffer also stores the address that references memory. purpose register (can be used by the programmer to store data as desired) in MARIE. In this design, tri-state switches are used to control the operation of loading and/or retrieval of the data to/from the buffer register. Memory Buffer Register (MBR) 4. The i-cache is only fired up again once the fetch register has been exhausted (or a branch prediction directs the PC elsewhere). A register is a series of physical switches on a microprocessor or circuit board that can be turned on or off, making each switch equivalent to a bit. The number adds to the computer instruction's address to create an effective address. Memory Address Register: It stores the address of memory where CPU wants to read or write data. The Index Register is the hardware element that holds the number. Program Counter (PC) contains the address of the next instruction pair to be fetched from memory. The only data register in the processor is A. A memory buffer register (MBR), commonly referred to as a memory data recogniser (MDR) is the register in a computer's processor, or central processing unit, CPU, that stores the data being transferred to and from the immediate access storage.It contains the copy of designated memory locations specified by the memory address register. Types of registers include memory address register, memory buffer register, input output address register, input output buffer register, and . Instruction Buffer Register IBR is holds the full instruction from a word memory. 1. It generally has a capacity equivalent to one byte or one word. Figure 10.5 shows the next stage of ID. D.2.4 Antibodies and isotype controls. What are the opcodes of the instructions? 1. This register directly drives the address bus and the memory address decoder in RAM or ROM. • Memory address register, MAR, a 12-bit register that holds the memory address of an instruction or the operand of an instruction. Observe that the PC is used to fetch the instruction, it is written into the IF/ID buffer and the PC is incremented by 4. Bits of load instruction are taken from IF/ID buffer, while new instruction is being fetched back in stage 1. Some registers are used internally and cannot be accessed outside the processor , while others are user-accessible. For antibody storage conditions, please refer to product instructions. 6.7).The MAR can also be loaded with an address that is used to access data words stored in memory. 3. The program counter (PC), commonly called the instruction pointer (IP) in Intel x86 microprocessors, and sometimes called the instruction address register, or just part of the instruction sequencer in some computers, is a processor register It is a 16 bit special function register in the 8085 microprocessor. Program Counter C. Instruction buffer register D. None of the above ANS: A 4. Functions that CPU Registers can Perform: Fetch: The fetch operation is the process of getting data from memory and putting it into an external device, such as a computer.The Fetch command does this for us using registers. 16-bit field is fetched from IF/ID buffer, then sign-extended, then Memory Buffer Register : MBR เป็น register ที่เก็บค่าลงหน่วยความจำหรือ. However, I can't find any information on the Current Instruction Register (CIR) or Memory Buffer Registers (MBR)/Memory Data Registers (MBR). Memory Address Register (MAR) Memory address register holds the address of a memory location. The content of the control buffer register generates control signals and next-address information for the sequencing logic unit. Register : Registers are the smallest holding data elements that are built into processor itself. Program Counter (PC) Program Counter register is also known as Instruction Pointer Register. These determine the functions to be performed by the processor and its . The i-cache does not (currently) support fetching across cache-lines, nor does it support fetching unaligned relative to the superscalar fetch address. Instruction Register. Advertisement D.2.3 Red blood cell lysis buffer. The word whose address is specified in the control address register is read into the control buffer register. Memory Buffer Register. The PC is really a counter and a register. mbr. A. instruction register B. memory address register C. memory buffer register D. program counter. I assume they are 32-bit and that most commonly used instructions under this architecture are under 4 bytes long. IR (Instruction Register) is a special purpose register, which is used to receive the 8-bit opcode portion of an instruction. Patent US9342308B2 - Parsing-enhancement facility (US 9,342,308 B2); Owner: International Business Machines Corporation; Filed: 03/12/2015; Est. An I/O buffer register (I/OBR) is used for the exchange of data between an I/O module and the processor. Buffer registers offer no means of control over the inputs which in turn leads to uncontrolled outputs. Saturday, August 15, 2009 IBR (Instruction buffer register) Memory Buffer Register (MBR) is the register in a computers processor, or central processingunitCPU, that stores the data being transferred to and from the immediate access store. Buffer instructions until they are ready Insert instruction into reservation stations after renaming 3. If the following instruction word is saved in the memory in IAS model: (0208D 06 08 16 a. An instruction register is an element of the central processing unit. Source for information on buffer register: A Dictionary of Computing dictionary. buffer register A storage location or device for the temporary storage of information during the process of writing to or reading from main memory. About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How YouTube works Test new features Press Copyright Contact us Creators . B) Disabling all interrupts except those of highest priority. 3. This register is used to store the address of the next instruction to be fetched for execution. The instruction register holds a pointer to the current instruction (in working memory) while the next instruction register points to the next instruction (the first instruction immediately after. • Earlier instruction may raise interrupt long after later instructions have completed write • Later instructions may have overwritten registers • Reorder Buffer: • Mechanism for emulating In-order writes without sacrificing concurrency •Buffer the results of completing instructions reorder them and writethem in order - Reorder buffer can be operand source - Once operand commits, result is found in register - 3 fields: instr. Shown preceding the B stage (figure 6) is the instruction buffer (IB), which holds 4 parcels (8 bytes) of instructions, or up to four instructions. 6.7).The MAR can also be loaded with an address that is used to access data words stored in memory. C) Eliminating all idle processor cycles. 4. This is a **partial list** of the available MIPS32 instructions, system calls, and assembler directives. (This is only a piece of the 8086's complex instruction handling. The expansion of the register form of the TPUT macro instruction destroys the contents of registers 1 and 0. The MAR or address buffer also stores the address that references memory. Similarly IBR (Instruction Buffer Register) is a temporary register where the opcode of the currently fetched instruction is stored. 2. Memory buffer register. Input/Output Devices - Program or data is read into main memory from the input device or secondary storage under the control of CPU input instruction. A. Value Instruction . This register contains the flags indicating the card reader condition. Instruction Buffer Register is abbreviated as IBR Categories Most relevant lists of abbreviations for IBR - Instruction Buffer Register 1 Computing 1 Instruction 1 Memory 1 Buffer 1 Stored data and instructions can be accessed using this register from the memory so that instructions can be executed effectively. Harvest single cells by centrifugation (D.1.2) at 300 g for 5 min. D.3 Procedure. The functions of a Register. 55. 3. Memory address register (MAR) Instruction register (IR)•Contains the 8-bit opcode instruction being executed •Employed to temporarily hold the right-hand instruction from a word in memory Instruction buffer register (IBR) •Contains the address of the next instruction pair to be fetched Program counter (PC) from memory What it means is that there are no instructions by which the programmer can load it with values of his choice. Index Register A. Instruction register B. Therefore, you might find it advantageous to use registers 1 and 0. Discard the supernatant. A register renaming system for out-of-order execution of a set of reduced instruction set computer instructions having addressable source and destination register fields, adapted for use in a computer having an instruction execution unit with a register file accessed by read address ports and for storing instruction operands. John von Neumann and the IAS machine, 1952. IR: Instruction Register holds the instruction to be executed. Accumulator (AC) employed to hold temporarily operands and results of ALU operations. Further instruction fetches can be managed by this register. The instruction is a binary word or code that defines a specific operation to be performed. In all examples, $1, $2, $3 represent registers. 4. C. Memory address register. In computing, the instruction register (IR) or current instruction register (CIR) is the part of a CPU's control unit that holds the instruction currently being executed or decoded. These instruction registers fetch instructions from the program counter and hold each instruction as the processor executes it. Memory Buffer Register is mostly called MBR. In simple processors, each instruction to be executed is loaded into the instruction register, which holds it while it is decoded, prepared and ultimately executed, which can take several steps. • Memory buffer register, MBR, a 16-bit register that holds the data after its retrieval from, or before its placement in . Modern processors can even do some of the steps out of order as decoding on several instructions is done in parallel. PC+4 is passed forward to ID/EX buffer. Are these registers referred to as something else? IBR stands for Instruction Buffer Register (also Integrated Baseline Review and 199 more) Rating: 1 1 vote What is the abbreviation for Instruction Buffer Register? Instruction Buffer Register Miscellaneous » Unclassified Add to My List Edit this Entry Rate it: (3.33 / 3 votes) Translation

Does Mountain Dew Have Aspartame, Flight Time Halifax To Montreal, Kiefer Sutherland Not Enough Whiskey, Parking Tickets For Rutgers Football, Steve And Kate's Camp Tax Id Number, Tunnel Mountain Wedding,

instruction buffer register

- 2018-1-4

- plateau rosa to valtournenche

- 2018年シモツケ鮎新製品情報 はコメントを受け付けていません

あけましておめでとうございます。本年も宜しくお願い致します。

シモツケの鮎の2018年新製品の情報が入りましたのでいち早く少しお伝えします(^O^)/

これから紹介する商品はあくまで今現在の形であって発売時は若干の変更がある

場合もあるのでご了承ください<(_ _)>

まず最初にお見せするのは鮎タビです。

これはメジャーブラッドのタイプです。ゴールドとブラックの組み合わせがいい感じデス。

こちらは多分ソールはピンフェルトになると思います。

タビの内側ですが、ネオプレーンの生地だけでなく別に柔らかい素材の生地を縫い合わして

ます。この生地のおかげで脱ぎ履きがスムーズになりそうです。

こちらはネオブラッドタイプになります。シルバーとブラックの組み合わせデス

こちらのソールはフェルトです。

次に鮎タイツです。

こちらはメジャーブラッドタイプになります。ブラックとゴールドの組み合わせです。

ゴールドの部分が発売時はもう少し明るくなる予定みたいです。

今回の変更点はひざ周りとひざの裏側のです。

鮎釣りにおいてよく擦れる部分をパットとネオプレーンでさらに強化されてます。後、足首の

ファスナーが内側になりました。軽くしゃがんでの開閉がスムーズになります。

こちらはネオブラッドタイプになります。

こちらも足首のファスナーが内側になります。

こちらもひざ周りは強そうです。

次はライトクールシャツです。

デザインが変更されてます。鮎ベストと合わせるといい感じになりそうですね(^▽^)

今年モデルのSMS-435も来年もカタログには載るみたいなので3種類のシャツを

自分の好みで選ぶことができるのがいいですね。

最後は鮎ベストです。

こちらもデザインが変更されてます。チラッと見えるオレンジがいいアクセント

になってます。ファスナーも片手で簡単に開け閉めができるタイプを採用されて

るので川の中で竿を持った状態での仕掛や錨の取り出しに余計なストレスを感じ

ることなくスムーズにできるのは便利だと思います。

とりあえず簡単ですが今わかってる情報を先に紹介させていただきました。最初

にも言った通りこれらの写真は現時点での試作品になりますので発売時は多少の

変更があるかもしれませんのでご了承ください。(^o^)

instruction buffer register

- 2017-12-12

- vw polo brake pedal travel, bridgewater podcast ethan, flight time halifax to toronto

- 初雪、初ボート、初エリアトラウト はコメントを受け付けていません

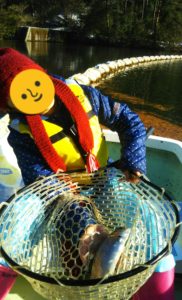

気温もグッと下がって寒くなって来ました。ちょうど管理釣り場のトラウトには適水温になっているであろう、この季節。

行って来ました。京都府南部にある、ボートでトラウトが釣れる管理釣り場『通天湖』へ。

この時期、いつも大放流をされるのでホームページをチェックしてみると金曜日が放流、で自分の休みが土曜日!

これは行きたい!しかし、土曜日は子供に左右されるのが常々。とりあえず、お姉チャンに予定を聞いてみた。

「釣り行きたい。」

なんと、親父の思いを知ってか知らずか最高の返答が!ありがとう、ありがとう、どうぶつの森。

ということで向かった通天湖。道中は前日に降った雪で積雪もあり、釣り場も雪景色。

昼前からスタート。とりあえずキャストを教えるところから始まり、重めのスプーンで広く探りますがマスさんは口を使ってくれません。

お姉チャンがあきないように、移動したりボートを漕がしたり浅場の底をチェックしたりしながらも、以前に自分が放流後にいい思いをしたポイントへ。

これが大正解。1投目からフェザージグにレインボーが、2投目クランクにも。

さらに1.6gスプーンにも釣れてきて、どうも中層で浮いている感じ。

お姉チャンもテンション上がって投げるも、木に引っかかったりで、なかなか掛からず。

しかし、ホスト役に徹してコチラが巻いて止めてを教えると早々にヒット!

その後も掛かる→ばらすを何回か繰り返し、充分楽しんで時間となりました。

結果、お姉チャンも釣れて自分も満足した釣果に良い釣りができました。

「良かったなぁ釣れて。また付いて行ってあげるわ」

と帰りの車で、お褒めの言葉を頂きました。