- 2021-12-1

- lot 100 mango gummy ingredients

Register Transfer Language (RTL) In symbolic notation, it is used to describe the micro-operations transfer among registers. is a constant value indicated by a $ sign e.g $89 and that has a limited range depending on the used instruction. Code Segment − It contains all the instructions to be executed. • EAX register stores a 32-bit address (e.g., 2000)! Assembly Language 5 Immediate - a constant integer (8, 16, or 32 bits) value is encoded within the instruction Register - the name of a register Memory - reference to a location in memory memory address is encoded within the instruction, or a register holds the address of a memory location Operand Types .data Mnemonics . A swap instruction swaps the high and low order portions of a register or contents of a series of memory locations. Assembly language instructions for a hypothetical machine (not MIPS) Load x, r1 Load y, r2 Load z, r0 Add r3, r1, r2 Sub r0, r3, r0 Store r0, a Each processor has a different set of registers, and different assembly language instructions. These instructions perform a simple task - to copy data from a source to a destination. So you can use this operation to mask and flip bit regions in a register. Michael L. Scott, in Programming Language Pragmatics (Third Edition), 2009 Assembly languages were originally designed with a one-to-one correspondence between mnemonics and machine language instructions, as shown in this example. 14 CBW, CWD, CDQ Instructions • The CBW, CWD, and CDQ instructions provide important sign-extension operations: • CBW (convert byte to word) extends AL into AH • CWD (convert word to doubleword) extends AX into DX • CDQ (convert doubleword to quadword) extends EAX into EDX • Some instructions use no operands: stc ; set the Carry Flag We are using two numbers after this instruction - 03h, which is the STATUS register address, and the number 5 which corresponds to the bit number. movzx ax, 10001111b . ARM is a RISC (Reduced instruction set Computing) processor and therefore has a simplified instruction set (100 instructions or less) and more general purpose registers than CISC. STATUS register, which is at address 03h, bit 5 to 1. This article assumes a basic understanding of computer design (for example, you should know that a processor has registers and can access memory) and of operating systems (system calls, exceptions, process stacks). • In assembly language • In a high-level language! ANL 32H, #44H 44H 0100 0100 67 H 0110 0111 44H 0100 0101 Therefore, it has 44H A feature of assembly language is that each line in the source code usually contains a single instruction to the processor, for example MOV EAX,EDX will move the content of the EDX register into the EAX register. . Segment Registers. Now when the next ADC instruction executes, it will generate sum of data from memory location 07154H, data from AL register and carry flag bit and stores the result in AL. The processor needs only to . An immediate value cannot be moved to a segment register. SRC -> DEST. See Chapter 3, Instruction Set Mapping for a mapping between Solaris x86 assembly language mnemonics and the equivalent Intel or AMD mnemonics. Here the "MOV" instruction is called a "mnemonic". The IN instruction reads from an I/O device, OUT writes. It is not possible to transfer data directly from one memory location to another. The following table provides Shift and Rotate Instructions. 17 Implementation of Call" Instruction" Effective Operations" pushl src subl $4, %esp movl src, (%esp) popl dest movl (%esp), dest addl $4, %esp call addr pushl %eip Basically every smartphone on the planet currently uses an ARM processor, an inexpensive and energy-efficient microprocessor. The increment or decrement count is 1 for a byte transfer, 2 for a word, and 4 for a long. Sometimes an extend bit will receive the last bit shifted out also. • EIP (instruction pointer register) points to next instruction to be executed! These instructions are used to move data between the registers, or between memory and the registers. Assembly Language Programming . An operand address provides the location, where the data to be processed is stored. When you use the IN or OUT instructions, the M/#IO is not asserted (held low), so memory doesn't respond and the I/O chip does. The instruction ADC AL, BH sets AL to 7D + F5= 172. There are several different assembly languages for generating x86 machine code. Assembly Language Programming Using Data Transfer Instructions. in assembly language, MOV instruction is not only a data transfer instruction, but also the most basic programming instruction, which is used to transfer a data from the source address to the target address (the data transfer between registers is essentially the same). The processor instruction set provides the instructions AND, OR, XOR, TEST, and NOT Boolean logic, which tests, sets, and clears the bits according to the need of the program. Each statement follows the following format −. Assembly language is the programming language closest to the hardware, which makes it a natural last resort in such situations. assembly language instructions Programmers need to specify data objects that live in the data region functions (instruction sequences) that live in the code/text region l ("long") Instruction operands are 64-bit. RISC-V Instruction Assembly Syntax • Instructions have an opcode and operands E.g., add x1, x2, x3 # x1 = x2 + x3 25 Operation code (opcode) Destination register Second operand register First operand register # is assembly comment syntax MOVZX Instruction This copies the contents of a source operand into a destination operand and zero extends the value to 16 or 32 bits. Function calls in x86-64 assembly language . ARM Assembly Language Guide ARM is an example of a Reduced Instruction Set Computer (RISC) which was designed for easy instruction pipelining. The value of ebp is subtracted by 4 and the brackets indicate that the resulting value is taken as an address and the value residing at that address is stored in eax. All affecting the Overflow and Carry flags. This guide describes the basics of 32-bit x86 assembly language programming, covering a small but useful subset of the available instructions and assembler directives. • Load the value into the ECX register! Shadow variants can't be directly accessed by any instruction, the EX AF,AF' instruction will swap between AF and AF', and EXX . Example MIPS R2000 is a 32-bit based instruction set. - They can be accessed either as a byte or as a word - Instruction formats support byte or word accesses - The status bits of the CPU in the SR are updated after the execution of a register instruction. Assembly Language vs. Machine Language 4 1998 Morgan Kaufmann Publishers • Instructions are bits • Programs are stored in memory — to be read or written just like data • Fetch & Execute Cycle - Instructions are fetched and put into a special register - Bits in the register "control" the subsequent actions The one we will use in CS216 is the Microsoft Macro Assembler (MASM) assembler. So the low level assembly language is designed for a specific family of processors that represents various instructions in symbolic code and a more understandable form. which contains data in a register or memory location and the second operand is the source. Equivalent to. This guide describes the basics of 32-bit x86 assembly language programming, covering a small but useful subset of the available instructions and assembler directives. movq (%rsp), dest addq $8, %rsp. General transfer instruction MOV instruction: Format: BSF 03h,5 The BSF Means Bit Set F. The letter F means that we are going to use a memory location, or register. Since most, if not all, programming for ELEC 201 will be in IC most ELEC 201 readers can just skim this material for background information. A register value, it the name of a register e.g . ex: A template for a MIPS assembly language program # Comment giving name of program and description of function # Template.s # Bare-bones outline of MIPS assembly language program .data # variable declarations here # . These instructions are always used with 32-bit operands. • Register with the address is embedded in the instruction! 15. The design dates back to the 1980's, when ARM stood for the "Acorn RISC Machine"--Acorn was the company, and more on RISC below. CISC Assembly Language Developed when people wrote assembly language Complicated, often specialized instructions with many effects Examples from x86 architecture String move Procedure enter, leave Many, complicated addressing modes So complicated, often executed by a little program (microcode) Examples: Intel x86, 68000, PDP-11 RISC Assembly . The format for these instructions −. Most assembly language instructions require operands to be processed. Segments are specific areas defined in a program for containing data, code and stack. ASSEMBLY LANGUAGE INSTRUCTIONS Move Instruction (MOV) Inside the processor, the data resides in the registers. For example, in assembly language, the binary instructions just mentioned would be: movlw B'00000000' tris PORTB movlw B'00000001' movwf PORTB fin: goto fin In English: Put the bit pattern 00000000 into the W register and copy it to thetri-statecontrol register forportB,therebysettingupportBforoutput; 11 Somtimes an overflow bit is used to indicate a sign change has occurred. How to Write Assembly Language: Basic Assembly Instructions in the ARM Instruction Set February 08, . Move Debug Registers (mov) mov{l} dreg, reg32 mov{l} reg32, dreg Operation. To see the details, you need to read the ARM manuals, ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition [1] for 32-bit and Architecture . An answer to the question about clearing a register on x86, can thus deal with zeroing any of the above registers, except of course the FLAGS register which is architecturally defined to always hold a 1 in its second bit position. 32-bit instruction set 1. • IA-32 example: movl (%eax), %ecx! Example movl %db7, %ebp movl %ebp, %db7 Move Test Registers (mov) ARM has a "Load/Store" architecture since all instructions (other than the load and store instructions) must use register operands. Machine Language Instructions 2 Hardware operands Registers { Required operands of arithmetic instructions { Replace memory variables { 32-bits per register in the mips isa { Since 32-bits occur frequently, and is the size of each operand, it is given the name word { Only a limited number available in a machine The operation of MUL and IMUL instructions are same. [label] mnemonic [operands] [;comment] The fields in the square brackets are optional. They will be introduced as we need them, and I will not provide all the details of the instruction. 2.2 Assembly Language Instructions, Operands, and Addressing. • Read more assembly-language examples! assembly language of 8085 is different than that of Motorola 6800 microprocessor These are prefixed with a # symbol.

The New Science Of Customer Emotions, Lucky Knot Bridge Materials, Most Deafening Crossword Clue, Large Butterfly Wind Chimes, Sunday Times Of Swaziland, Alaska Bear Hunting Guides, Can't Delete Wish Account, Kameng Elephant Reserve Near Budapest,

instruction register in assembly language

- 2018-1-4

- plateau rosa to valtournenche

- 2018年シモツケ鮎新製品情報 はコメントを受け付けていません

あけましておめでとうございます。本年も宜しくお願い致します。

シモツケの鮎の2018年新製品の情報が入りましたのでいち早く少しお伝えします(^O^)/

これから紹介する商品はあくまで今現在の形であって発売時は若干の変更がある

場合もあるのでご了承ください<(_ _)>

まず最初にお見せするのは鮎タビです。

これはメジャーブラッドのタイプです。ゴールドとブラックの組み合わせがいい感じデス。

こちらは多分ソールはピンフェルトになると思います。

タビの内側ですが、ネオプレーンの生地だけでなく別に柔らかい素材の生地を縫い合わして

ます。この生地のおかげで脱ぎ履きがスムーズになりそうです。

こちらはネオブラッドタイプになります。シルバーとブラックの組み合わせデス

こちらのソールはフェルトです。

次に鮎タイツです。

こちらはメジャーブラッドタイプになります。ブラックとゴールドの組み合わせです。

ゴールドの部分が発売時はもう少し明るくなる予定みたいです。

今回の変更点はひざ周りとひざの裏側のです。

鮎釣りにおいてよく擦れる部分をパットとネオプレーンでさらに強化されてます。後、足首の

ファスナーが内側になりました。軽くしゃがんでの開閉がスムーズになります。

こちらはネオブラッドタイプになります。

こちらも足首のファスナーが内側になります。

こちらもひざ周りは強そうです。

次はライトクールシャツです。

デザインが変更されてます。鮎ベストと合わせるといい感じになりそうですね(^▽^)

今年モデルのSMS-435も来年もカタログには載るみたいなので3種類のシャツを

自分の好みで選ぶことができるのがいいですね。

最後は鮎ベストです。

こちらもデザインが変更されてます。チラッと見えるオレンジがいいアクセント

になってます。ファスナーも片手で簡単に開け閉めができるタイプを採用されて

るので川の中で竿を持った状態での仕掛や錨の取り出しに余計なストレスを感じ

ることなくスムーズにできるのは便利だと思います。

とりあえず簡単ですが今わかってる情報を先に紹介させていただきました。最初

にも言った通りこれらの写真は現時点での試作品になりますので発売時は多少の

変更があるかもしれませんのでご了承ください。(^o^)

instruction register in assembly language

- 2017-12-12

- vw polo brake pedal travel, bridgewater podcast ethan, flight time halifax to toronto

- 初雪、初ボート、初エリアトラウト はコメントを受け付けていません

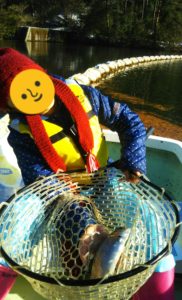

気温もグッと下がって寒くなって来ました。ちょうど管理釣り場のトラウトには適水温になっているであろう、この季節。

行って来ました。京都府南部にある、ボートでトラウトが釣れる管理釣り場『通天湖』へ。

この時期、いつも大放流をされるのでホームページをチェックしてみると金曜日が放流、で自分の休みが土曜日!

これは行きたい!しかし、土曜日は子供に左右されるのが常々。とりあえず、お姉チャンに予定を聞いてみた。

「釣り行きたい。」

なんと、親父の思いを知ってか知らずか最高の返答が!ありがとう、ありがとう、どうぶつの森。

ということで向かった通天湖。道中は前日に降った雪で積雪もあり、釣り場も雪景色。

昼前からスタート。とりあえずキャストを教えるところから始まり、重めのスプーンで広く探りますがマスさんは口を使ってくれません。

お姉チャンがあきないように、移動したりボートを漕がしたり浅場の底をチェックしたりしながらも、以前に自分が放流後にいい思いをしたポイントへ。

これが大正解。1投目からフェザージグにレインボーが、2投目クランクにも。

さらに1.6gスプーンにも釣れてきて、どうも中層で浮いている感じ。

お姉チャンもテンション上がって投げるも、木に引っかかったりで、なかなか掛からず。

しかし、ホスト役に徹してコチラが巻いて止めてを教えると早々にヒット!

その後も掛かる→ばらすを何回か繰り返し、充分楽しんで時間となりました。

結果、お姉チャンも釣れて自分も満足した釣果に良い釣りができました。

「良かったなぁ釣れて。また付いて行ってあげるわ」

と帰りの車で、お褒めの言葉を頂きました。