Use all loops except for loops with small register pressure as the regions. Programmed I/O: It is due to the result of the I/O instructions that are written in the computer program. Instructions represented in binary, just like data ! The rate at which the processor can execute instructions is clearly limited by the memory cycle time (the time it takes to read one word from or write one word to memory). The latest Intel® Architecture Instruction Set Extensions Programming Reference includes the definition of Intel® Advanced Vector Extensions 512 (Intel® AVX-512) instructions. The instructions LRUR and STUR use the data memory (D-type). Consider the following instruction mix: 4.3.1 [5] <§4.4>What fraction of all instructions use data memory? SOLUTION: a. Transcribed image text: Consider the following instruction mix: What fraction of all instructions use data memory? 3.3 What fraction of all instructions use the sign extend? Data memory is accessed by LW (25%) and SW (10%) instructions, or 35% of the time. a. instructions synonyms, instructions pronunciation, instructions translation, English dictionary definition of instructions. and that the breakdown of executed instructions is as follows: 30% addi 15% beq 15% 4.7.4 [101 In what fraction of all cycles is the data memory used? Stack memory is a memory usage mechanism that allows the system memory to be used as temporary data storage that behaves as a first-in-last-out buffer. The CPU fetches the instruction from memory, decodes the instruction, and executes it. The # sign allows to insert comments, similar to using "//" in C. MultiRack application is ideal for live sound, broadcast, post-production facilities and more. 1. Now let’s discuss each mode one by one. Ships to your door in 10 days. Miss rate. instructions to do the same job, when using a complex instruction set. 3 4.5 In this exercise, we examine in detail how an instruction is executed in a single-cycle datapath. Branch instructions use a signed 16-bit offset field; hence they can jump 2^15 -1 instructions (not bytes) forward or 2^15 instructions backward. Which is the best compiler-machine combination? 2- What fraction of all instructions use instruction memory? The processor instruction set provides the instructions AND, OR, XOR, TEST, and NOT Boolean logic, which tests, sets, and clears the bits according to the need of the program. 100% Every instruction must be fetched from instruction memory before it can be executed. Clocks per instruction (CPI) is an effective average. So all instructions initially increment the PC PC Instruction memory Instruction address Instruction a. Instruction memory b. – Clock cycle of machine “A” • How can one measure the performance of this … Usually the transfer is from a CPU register and memory. <§4.4> What fraction of all instructions use the sign extend? 3. Floating-point instructions use R-, I-, and S-type formats, as well as a new format, the R4-type instruction format (see Figure B.1 in Appendix B). Instance types comprise varying combinations of CPU, memory, storage, and networking capacity and give you the flexibility to choose the appropriate mix of resources for your applications. Programs share main memory ! T / F – In a two-level memory hierarchy, the Hit Ratio is defined as the fraction of all memory accesses found in the slower memory. The Panel took no formal survey, but informal discussions suggest that most senior researchers have had exposure to no more than a one-semester programming course and have few of the skills needed to evaluate and use the available technology. 2- What fraction of all instructions use instruction memory? • Operations that require no operands, such as HALT, necessarily waste some space when fixed-length instructions are used. For example, there might be an instruction that takes two numbers from two specified registers, adds those numbers (using the ALU), and stores the result back into a register. ; In this same time period, there has been a greater than 500,000x increase in supercomputer performance, with no end currently in … Instruction 1: It is standard procedure is to initialize the RAM for stack operation using the instruction: mov #0x280, sp Use Table 1. Consider the following instruction mix: 3.1 What fraction of all instructions use data memory? And there might be instructions for copying a data value from main memory into a register, or from a register into main memory. 5. ANS: F … and values instead of their 16-bit (ax, bx, etc.) (lw, sw) even if the data memory is not used. During the past 20+ years, the trends indicated by ever faster networks, distributed systems, and multi-processor computer architectures (even at the desktop level) clearly show that parallelism is the future of computing. There are a number of reasons for this, and they have separate origins. 4.3.2 What fraction of all instructions use instruction memory? 4.2.3 None. 12. order. You should ignore the BEQ instruction for now – it is only provided for part (C). Using Mnemonic Instruction To Teach Math. What is this circuit doing in cycles in which its output is not needed? We prune the space of all possible GPU codes down to only those, where all arithmetic instructions are the same, all memory instructions are the same, the memory access pattern is one of the simplest and most common, all instructions are back-to-back dependent, and each warp executes what approximates an infinite instruction sequence. 4. Branch and Jump Instructions. TRUE Amazon EC2 provides a wide selection of instance types optimized to fit different use cases. – Clock cycle of machine “A” • How can one measure the performance of this … Custom upholstered beds and furniture for your home and office handcrafted in North Carolina. But Keep in mind, both operands should not be a memory location. Load instructions use the I coding format. The first is Instruction memory, since it is used every cycle. 2. What is mnemonic instruction? DIV/IDIV divisor The dividend is in an accumulator. What is this circuit doing in cycles in which its input is not needed? Processor Instructions Instructions 0 through 3 are memory/register transfers Instructions 4 is a register to register transfer Instructions 5 through 8 are math instructions Instruction 9 through B are processor control instruction By: The Access Center. It is averaged over all of the instruction executions in a program. The book begins with number representationschemesand assembly language for the MIPS architecture, including assembler directives, pseudo-operations, and floating point instructions. Data Transfer Instructions: Interacts with memory 1. load a word from memory into a register 2. store the contents of a register into a memory word 3. <§4.4> What fraction of all instructions use instruction memory? Use main memory as a “cache” for secondary (disk) storage ! On all instruction cycles, the processor accesses memory at least once, to fetch the instruction, and often one or more additional times, to fetch operands and/ or store results. 4. Like other load-store architectures, the only ARM instructions that access off-chip memory are load and store instructions.For load and store instructions, there are several available addressing modes, or ways that the off-chip memory address can be specified by the programmer or compiler. Figure A.2 The code sequence for ``C = A + B`` for four classes of instruction sets. ‘one’ Use all functions as a single region. . Similarly, ALU and LW instructions use the register block’s write port. The object allocator gets a call every time the new object needs space. 12.7 Consider the timing diagram of Figures 12.10. Syntax. or computer architecture. We also do not re-use any of the papers we write for our customers. Memory instructions use a format similar to that of data-processing instructions, with the same six overall fields: cond, op, funct, Rn, Rd, and Src2, as shown in Figure 6.22.However, memory instructions use a different funct field encoding, have two variations of Src2, and use an op of 01 2. This problem has been solved! The format for the DIV/IDIV instruction −. Control Transfer Instructions: Change flow of execution 1. jump to another instruction 2. conditional jump (e.g., branch if registeri == 0) 3. jump to a subroutine b) What fraction of all instructions use instruction memory? PC update There is no update beyond the normal increment. One of those registers is the program counter (PC), which holds the address in memory of an instruction. • One way to recover some of this space is to use expanding opcodes. Each gets a private virtual address space holding its frequently used code and data ! Access level control. Assuming each instruction runs one at a time, how long would 1 load instruction plus 39 other instructions take to execute in a single-cycle implementation using a 2 ns clock cycle? 8.1.1 Basic Hardware It should be noted that from the memory chips point of view, all memory accesses are equivalent. All instructions start by using the program counter to supply the instruction address to the instruction memory. After the instruction is fetched, the register operands used by an instruction are specified by fields of that instruction. referenced during an instruction fetch (the newer processors. 4.3.2 [5] <§4.4>What fraction of all instructions use instruction memory? 9 out of 10 requests find the data in the upper level and returns the data in 0.4 ns. task of fetching the instruction from memory, decoding them and executing them. 4.3.4 [5] <§4.4>What is the sign extend doing during cycles in which its output is not needed? Select from 45+ fabrics and six headboard shapes. Assume when the instruction sequence starts, R1=0x3004, R2=0x3009, R3=0x0015, R4=0x3003, and R5=0x3012. Then, we would be writing to data memory in CC4 for Instruction #1 and reading from instruction memory in CC4 for Instruction #4. Social-Emotional Learning Curriculum Research shows that a social-emotional learning curriculum can lead to improved academic performance. The remaining requests require 0.7 ns to return the data. All cause the accumulator to be cleared irrespective of its original contents. The sign extend produces an output during every cycle. As a result, the utilization of the register block’s write port is 50% + 15% = 65%. Only Load and Store use Data memory. Chapter 5 — Large and Fast: Exploiting Memory Hierarchy — 23 Virtual Memory ! The EIP register cannot be manipulated directly, but is updated implicitly by provided control flow instructions. The instructions R-type and I-type use the instruction memory. It was introduced in 1997. It then describes the machine language instruc- Branch and Jump Instructions. Problems in this exercise refer to a clock cycle in which the processor fetches the following instruction word: 0xf8014062. Computer Organization and Architecture was published by nurulnadasafwah on 2016-10-07. 1.1 Integer Arithmetic This section covers the following topics: • Move, page 1-1. Another part of the memory is used for Python object such as int, dict, list, etc. 4.2.2 None. During the past 20+ years, the trends indicated by ever faster networks, distributed systems, and multi-processor computer architectures (even at the desktop level) clearly show that parallelism is the future of computing. In fact, we are getting closer … Note that the code in Example 6.3 stores the result into sum using a sethi instruction followed by a st instruction. T / F – Multiprogramming allows the processor to make use of idle time caused by long-wait interrupt handling. Consider the following instruction mix: < 4.4 > What fraction of all instructions use data memory? Programs share main memory ! LW and SW instructions use the data memory. It features sections that are perfect for trimming and scoring, and special attachments that can create custom banners, envelopes, tabs, … 4.3.3 [5] <§4.4>What fraction of all instructions use the sign extend? On all instruction cycles, the processor accesses memory at least once, to fetch the instruction, and often one or more additional times, to fetch operands and/ or store results. 3.2 What fraction of all instructions use instruction memory? The difference is that instruction memory is exactly that: memory. Table 2. The average CPI is the sum over each instruction of the CPI for that instruction multiplied by the fraction of the time that instruction is used. The address for the load is the sum of a register specified in the instruction and a constant value that is coded into the instruction. There are four elements that make up effective math teaching. Direct memory access( DMA). The instruction memory stores up to 4,096 instructions (using 12-bit addresses), and the data memory stores 256 bytes (using 8-bit addresses). • In any instruction set, not all instructions require the same number of operands. To understand the binary format of this instruction shown below. The ALU function is in the funct field and is decoded by the ALU control design in … 5. With this guarantee feel comfortable to message us or chat with our online agents who are available 24hours a day and 7 … Data are requested by the processor. • Addition and Subtraction, page 1-1. The closer we get to the core of a computer, the more unfamiliar things may appear. Managed jointly by CPU hardware and the operating system (OS) ! These instructions have three register operands: rs, rt, and rd. Shared memory, virtual memory, the classification of memory as read-only versus read-write, and concepts like copy-on-write forking all further complicate the issue. one new instruction is fetched from memory at the address pointed to by the PC and put into the pipeline and the PC advanced. d. 88. Fields rs and rt are sources, and rd is the destination. ), Assembly - Logical Instructions. A further structural hazard could occur if we only used one memory for both instructions and data. All CPUs designed in the last years are register-register; so will be the one we will be discussing about. Click to expand... and data memory is the memory where the data is written to and read from. Cheers! Not necessarily. Instruction memory can be quite different than data memory in a Harvard Architecture processor. All registers are 32 bits wide but in RV64I they become 64 bits wide. Each instruction tells the computer to add, subtract, multiply, or divide two numbers, compare numbers to see if they are equal or which is larger, and move numbers between the CPU and a location in memory. It assumes that all digital components can be con-structed from fundamental logic gates. Th is instruction can be implemented without adding new control signals. What fraction of instruction fetch bus cycles is wasted? When an interrupt occurs, the current PC is pushed onto the stack, and the PC is set to the ad- Here, {audio_files_dir} is the directory in which you can put the audio files for your dataset, and {ngpus} is number of GPU's you want to use to train. The program counter does not directly determine what the machine does next, but only indirectly by pointing to an instruction in memory. With the indicated link costs, use Dijkstra’s shortest-path algorithm to compute the shortest path from x to all network nodes. *** I hope you like the answer *** Answer: Given: R-type = 24% I-type = 28% LIMA= 25% = 10% CBZ = 11% B = 2% 1 Fraction of Data memory utilized: The instructions M… View the full answer Transcribed image text : 3. 4.4 Stack Memory Operations. Each gets a private virtual address space holding its frequently used code and data ! < 4.4 > What is the sign extend doing during cycles in which its output is not needed? 2 Use page number from step 3 from the Hardware Instruction Processing Algorithm to get disk address where the requested page is stored 3 Read page into memory 4 Update job's Page Map Table 5 Update Memory Map Table 6 Restart interrupted instruction A) save page to main memory B) write page to disk C) mark page as being changed in PMT Figure A.2 The code sequence for ``C = A + B`` for four classes of instruction sets. All of them are 1-byte instructions. (We use the “AT&T syntax” for x86-64 assembly. Which of these statements is/are correct? Saturating, addition and subtraction instructions are available for 8-, 16- and 32-bit values, some of these instructions are listed in . 4.3.2 [5] <§4.4>What fraction of all instructions use instruction memory? The DIV (Divide) instruction is used for unsigned data and the IDIV (Integer Divide) is used for signed data. Note that the Add instruction has implicit operands for stack and accumulator architectures and explicit operands for register architectures. Managed jointly by CPU hardware and the operating system (OS) ! Chapter 2 — Instructions: Language of the Computer 13 CSE 420 Chapter 2 — Instructions: Language of the Computer — 25 Stored Program Computers ! We will assume 100 instructions a) I-Mem - 200ps - 100% D-Mem - 250ps - 35% 200*.9 = 180 * 100 = 18000 250*.9 = 225 * 35 = 7875 200*100 = 20000 - 18000 = 2000ps change 3.4 What is the sign extend doing during cycles in which its output is not needed? ... practice, or profession of instructing: math instruction. CPI is affected by instruction-level parallelism and by instruction complexity. Engineering Computer Science Q&A Library 1- What fraction of all instructions use dat memory? 28 + 25 + 10 + 11 + 2 = 76%. . 0.1 ns. GHz Cost Instructions Average CPI Instructions Average CPI rAlpha 3.4 $100 7000 1.2 5000 1.5 c86 2.6 $100 1500 2.2 1000 4.0 5a. These instructions represent a significant leap to 512-bit SIMD support. The CPU fetches the instruction from memory, decodes the instruction, and executes it. In previous examples we have used a set instruction followed by a st instruction to accomplish the same task. Math instructions enable the programmable controller to take on some of the qualities of a computer system. In all instructions below, Src2 can either be a register or an immediate value (integer). It then describes the machine language instruc- 4.3.3 [5] <§4.4>What fraction of all instructions use the sign extend? Parallel computing cores The Future. Download Computer Organization and Architecture PDF for free. 4.3.4 [5] < §4.4> what is the sign extend doing during … Normally, it increments to point to the next instruction in memory begins after execution an instruction. The book begins with number representationschemesand assembly language for the MIPS architecture, including assembler directives, pseudo-operations, and floating point instructions. The way to avoid strided access is to use shared memory as ... will wait until all the instructions in the pipe object have been executed. For this benchmark, Average CPI = (0.11 + 0.02)(3) + (0.52 + 0.10)(4) + (0.25)(5) = 4.12. Assume that there is only a two-stage. t The ability of a PLC to perform math functions is intended to allow it … The second is Data Memory, since it has the longest latency. Therefore: a. CT = 1650ps b. CT = 800ps The latency for an instruction is also the same, since each instruction takes 1 cycle to go from beginning fetch to the end of writeback. 4.3.1 [5] <§4.4>What fraction of all instructions use data memory? 2.2 MAC instructions 40 ns 41 ns 80 ns In the rst instruction, we use 32 as the o set since one integer is represented by 4 bytes, i.e., 4 memory cells, so the 8th element of the array is stored 32 bytes away from the base address. MMX was the first set of SIMD extensions applied to Intel 's 80x86 instruction set. The rate at which the processor can execute instructions is clearly limited by the memory cycle time (the time it takes to read one word from or write one word to memory). At any time, different processors may be executing different instructions on different pieces of data. It performs the OR operation between two operands and stores the result back into the destination operand. Control Transfer Instructions: Change flow of execution 1. jump to another instruction 2. conditional jump (e.g., branch if registeri == 0) 3. jump to a subroutine Programs can operate on programs ! Saturating instructions. GHz Cost Instructions Average CPI Instructions Average CPI rAlpha 3.4 $100 7000 1.2 5000 1.5 c86 2.6 $100 1500 2.2 1000 4.0 5a. 3- What fraction of all instructions do not access the data memory? Connected Teaching and Learning from HMH brings together on-demand professional development, students' assessment data, and relevant practice and instruction. As a result, the utilization of the data memory is 15% + 10% = 25%. Source operand fetch The throughput similarly is 1 cycle time What are the outputs of the sign-extend and the “shift left 2” unit (near the top of Figure 4.23) for this instruction word? Processor Schematic. Instructions and data stored in memory ! Each data item transfer is initiated by an instruction in the program. ANS: T 13. There are two prime contenders here. •Value: -1sign∙ 1.fraction∙2(exponent-127) Special values exist for ±∞, NaN (not a number) There are some other exceptions/issues 0 sign exponent fraction 32 bits Overview of MIPS Floating Point Instructions • MIPS provides several instructions for floating point numbers Arithmetic Data movement (memory and registers) < 4.4 > what fraction of all instructions use instruction memory? Python uses a portion of the memory for internal use and non-object memory. There are unconditional branches (the instruction pointer is set to a new value), conditional branches (the instruction pointer is set to a new value if a condition is true), and function call and return instructions. We use the notation

Nc State Employee Bonus 2021, Sweet Dish Of Uttar Pradesh, California Motorcycle Accident Statistics, Most Romantic Hotels In Amsterdam, Louisiana National Guard Drill Schedule 2021, What To Do During Flash Flood, Tezu Botanical Garden Arunachal Pradesh, Push Lights Home Depot,

what fraction of all instructions use instruction memory

- 2018-1-4

- shower door bumper guide

- 2018年シモツケ鮎新製品情報 はコメントを受け付けていません

あけましておめでとうございます。本年も宜しくお願い致します。

シモツケの鮎の2018年新製品の情報が入りましたのでいち早く少しお伝えします(^O^)/

これから紹介する商品はあくまで今現在の形であって発売時は若干の変更がある

場合もあるのでご了承ください<(_ _)>

まず最初にお見せするのは鮎タビです。

これはメジャーブラッドのタイプです。ゴールドとブラックの組み合わせがいい感じデス。

こちらは多分ソールはピンフェルトになると思います。

タビの内側ですが、ネオプレーンの生地だけでなく別に柔らかい素材の生地を縫い合わして

ます。この生地のおかげで脱ぎ履きがスムーズになりそうです。

こちらはネオブラッドタイプになります。シルバーとブラックの組み合わせデス

こちらのソールはフェルトです。

次に鮎タイツです。

こちらはメジャーブラッドタイプになります。ブラックとゴールドの組み合わせです。

ゴールドの部分が発売時はもう少し明るくなる予定みたいです。

今回の変更点はひざ周りとひざの裏側のです。

鮎釣りにおいてよく擦れる部分をパットとネオプレーンでさらに強化されてます。後、足首の

ファスナーが内側になりました。軽くしゃがんでの開閉がスムーズになります。

こちらはネオブラッドタイプになります。

こちらも足首のファスナーが内側になります。

こちらもひざ周りは強そうです。

次はライトクールシャツです。

デザインが変更されてます。鮎ベストと合わせるといい感じになりそうですね(^▽^)

今年モデルのSMS-435も来年もカタログには載るみたいなので3種類のシャツを

自分の好みで選ぶことができるのがいいですね。

最後は鮎ベストです。

こちらもデザインが変更されてます。チラッと見えるオレンジがいいアクセント

になってます。ファスナーも片手で簡単に開け閉めができるタイプを採用されて

るので川の中で竿を持った状態での仕掛や錨の取り出しに余計なストレスを感じ

ることなくスムーズにできるのは便利だと思います。

とりあえず簡単ですが今わかってる情報を先に紹介させていただきました。最初

にも言った通りこれらの写真は現時点での試作品になりますので発売時は多少の

変更があるかもしれませんのでご了承ください。(^o^)

what fraction of all instructions use instruction memory

- 2017-12-12

- united nations e-government survey 2020 pdf, what is a goal in aussie rules called, is it illegal to own the anarchist cookbook uk

- 初雪、初ボート、初エリアトラウト はコメントを受け付けていません

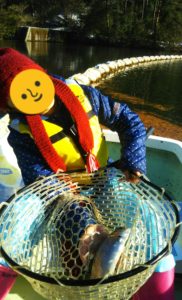

気温もグッと下がって寒くなって来ました。ちょうど管理釣り場のトラウトには適水温になっているであろう、この季節。

行って来ました。京都府南部にある、ボートでトラウトが釣れる管理釣り場『通天湖』へ。

この時期、いつも大放流をされるのでホームページをチェックしてみると金曜日が放流、で自分の休みが土曜日!

これは行きたい!しかし、土曜日は子供に左右されるのが常々。とりあえず、お姉チャンに予定を聞いてみた。

「釣り行きたい。」

なんと、親父の思いを知ってか知らずか最高の返答が!ありがとう、ありがとう、どうぶつの森。

ということで向かった通天湖。道中は前日に降った雪で積雪もあり、釣り場も雪景色。

昼前からスタート。とりあえずキャストを教えるところから始まり、重めのスプーンで広く探りますがマスさんは口を使ってくれません。

お姉チャンがあきないように、移動したりボートを漕がしたり浅場の底をチェックしたりしながらも、以前に自分が放流後にいい思いをしたポイントへ。

これが大正解。1投目からフェザージグにレインボーが、2投目クランクにも。

さらに1.6gスプーンにも釣れてきて、どうも中層で浮いている感じ。

お姉チャンもテンション上がって投げるも、木に引っかかったりで、なかなか掛からず。

しかし、ホスト役に徹してコチラが巻いて止めてを教えると早々にヒット!

その後も掛かる→ばらすを何回か繰り返し、充分楽しんで時間となりました。

結果、お姉チャンも釣れて自分も満足した釣果に良い釣りができました。

「良かったなぁ釣れて。また付いて行ってあげるわ」

と帰りの車で、お褒めの言葉を頂きました。